About Department

Department of Electronics Engineering (VLSI Design and Technology) was started in the year 2023. The department offers 4 years Under Graduate (UG). The student intake for the UG programme is 60. The curriculum and syllabus for the programmes offered in the department are designed as per the Regulation 2022 of the autonomous system. The curriculum is designed to achieve a balance between depth of knowledge acquired through specialization and breadth of knowledge gained through exploration. The undergraduate degree courses offered by the department provide a comprehensive foundation in the core topics of electronics coupled with areas of specialization relevant to emerging engineering challenges of VLSI. The curriculum has been designed to create professional electronics engineers, who can serve in the fields of core electronics engineering, VLSI and other related fields.

Vision

To emerge as a distinguished center of academic excellence, offering exceptional education in Electronics Engineering, with a distinct focus on VLSI design and advanced research.

Mission

- To nurture and develop professionals and technology leaders who uphold the highest standards of professional ethics in the realm of Electronics Engineering, with a focused specialization in VLSI design.

- To address the evolving needs of society by pushing the boundaries of disciplinary and multidisciplinary research in the field of Electronics Engineering, with our specialized focus on VLSI design.

The PEOs of UG Programmes

-

PEO1: To empower graduates with the skills and knowledge necessary to achieve successful

technical and professional career growth.

-

PEO2: To equip graduates with a profound understanding of the scientific, mathematical, and

engineering fundamentals relevant to Electronics Engineering, with a specialized focus on

VLSI design.

-

PEO3: To develop graduates who possess a commitment to lifelong learning, demonstrate

creativity and innovation, and exhibit ethical and professional behavior, all while

addressing the evolving needs of society.

Programme Outcomes (POs)

-

PO1: Engineering knowledge: Apply the knowledge of mathematics, science, engineering

fundamentals, and an engineering specialization to the solution of complex engineering

problems.

-

PEO2: Problem analysis: Identify, formulate, review research literature, and analyze complex

engineering problems reaching substantiated conclusions using first principles of

mathematics, natural sciences, and engineering sciences.

-

PO3: Design /development of solutions: Design solutions for complex engineering problems and

design system components or processes that meet the specified needs with appropriate

consideration for the public health and safety, and the cultural, societal, and

environmental considerations.

-

PO4: Conduct investigations of complex problems: Use research-based knowledge and research

methods including design of experiments, analysis and interpretation of data, and synthesis

of the information to provide valid conclusions.

-

PO5: Engineering Tool Usage: Create, select and apply appropriate techniques, resources

and modern engineering & IT tools, including prediction and modelling recognizing

their limitations to solve complex engineering problems.

-

PO6: The Engineer and The World: Analyze and evaluate societal and environmental

aspects while solving complex engineering problems for its impact on sustainability

with reference to economy, health, safety, legal framework, culture and environment.

-

PO7: Ethics: Apply ethical principles and commit to professional ethics, human values,

diversity and inclusion; adhere to national & international laws.

-

PO8: Individual and Collaborative Team work: Function effectively as an individual, and

as a member or leader in diverse/multi-disciplinary teams.

-

PO9: Communication: Communicate effectively and inclusively within the engineering

community and society at large, such as being able to comprehend and write effective

reports and design documentation, make effective presentations considering cultural,

language, and learning differences.

-

PO10: Project Management and Finance: Apply knowledge and understanding of

engineering management principles and economic decision-making and apply these to

one’s own work, as a member and leader in a team, and to manage projects and in

multidisciplinary environments.

-

PO11: Life-Long Learning: Recognize the need for, and have the preparation and ability for

i) independent and life-long learning ii) adaptability to new and emerging technologies

and iii) critical thinking in the broadest context of technological change.

Programme Specific Outcomes (PSOs)

Engineering Graduates will be able to:

-

PSO1: To develop graduates who are capable of solving complex engineering problems by

applying their engineering knowledge in the fields of AI (Artificial Intelligence), IoT

(Internet of Things), Signal Processing, VLSI design and related fields.

-

PSO2: To develop graduates who possess the capability to design system components and

develop products that meet the specific needs of the industry and society in the field of

Electronics Engineering, with a specialized focus on VLSI design.

-

PSO3: To develop graduates who possess essential interpersonal skills and attitudes required

for ethical leadership and effective teamwork, including effective listening and

communication, presentation skills, team building, and assertiveness.

Department Contact

From the Hod's Desk

Dr. T.Baranidharan

Professor & Head

AICTE Faculty ID:1-461790295 ;| College ID: KSREI02

LinkedIn Profile | IRINS Profile| ProfileMail-ID: [email protected]

Dr. T. Baranidharan has more than 18 years of teaching experience. He graduated with a B.E. degree in Electronics and Instrumentation Engineering from shanmugha college of Engineering, Bharathidasan University, Tiruchirappalli in the year 2003. He completed his post-graduation in Applied Electronics from Thanthai Periyar Government Institute of Technology at Anna University in 2005. He received his Ph.D. from Anna University, Chennai in 2013. He published 13 papers in reputed international journals. He presented several papers in various International & National Conferences. He is a recognized research supervisor at Anna University Chennai. Currently, 01 candidates have completed their Ph.D. under his guidance and 4 Ph.D. research scholars are pursuing currently. He organized several seminars, workshops, and conferences.

Faculty List

2025-26 - Click here

Our Intellectuals

Dr. S.Gomathi

Associate Professor & Vacation Co-ordinator

VLSI Design & Technology

Saranya C

Assistant Professor

VLSI Design & Technology (Low power VLSI)

Rajavenkatesan T

Assistant Professor

VLSI Design & Technology (VLSI Testing)

Poornakumar D

Assistant Professor

VLSI Design & Technology (Low Power VLSI)

Dr.S.Pradeep

Assistant Professor

VLSI Design & Medical Image Processing

Sureshkumar A

Assistant Professor

VLSI Design & Technology

Our Non-Teaching Staffs

Gokul S

Lab Technician

Elango A

Lab Technician

Tharani G

Programmer

Chitra s

Lab Attender

Curriculum & Syllabus

Under-Graduate - Electronics Engineering (VLSI Design and Technology)

| S.No | Name of the Faculty | Name of the Course & Module | Objective | Innovation in Teaching and Learning(Experiential Learning/Participative Learning) | Web page content Link-Proof |

|---|---|---|---|---|---|

| 1. | Dr.S.Pradeep | 60 EV 302 - Circuit Analysis | To apply and verify Thevenin's and Norton's theorems by simplifying complex circuits and comparing the calculated values of voltage and current with those obtained through simulation | Simulation | Click Here |

| 2. | Mr.T.Rajavenkatesan | 60 EV 301 - Electronic Circuits | The objective of using EdPuzzle for a "voltage series feedback amplifier" topic is to actively engage students with a video lesson by embedding interactive questions, ensuring they comprehend key concepts. | Ed-Puzzle | Click Here |

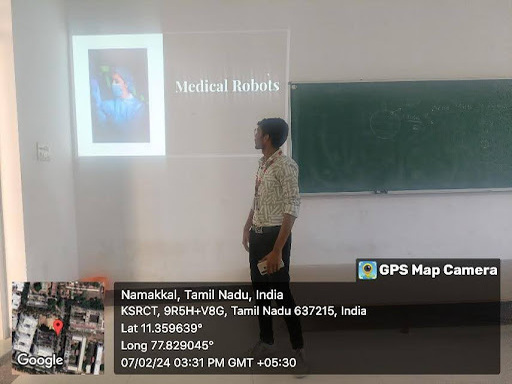

| 3. | Mrs.C.Saranya | 60 EV 502 - VLSI and Chip Design | The objective of a seminar on "RTL to GDS" is to provide a comprehensive understanding of the entire digital chip design flow, from the initial Register-Transfer Level (RTL) design to the final GDSII layout file used for fabrication. | Seminar | Click Here |

| 4. | Mr.D.Poorna Kumar | 60 EV 303 - Digital System Design | To demonstrate the fundamental principles of logic gates (AND, OR, NOT) through a role-play, where each participant embodies a gate and collectively processes inputs to produce a final output, illustrating how these basic components form the building blocks of digital circuits. | Role Play | Click Here |

Video Lectures

Circuit Analysis

VLSI and Chip Design

Digital System Design

Digital Signal Processing

| S.No. | Date | Name of Course | Industry Association |

|---|---|---|---|

| 1. | 02.07.2025 | 60 EV E13 & ASIC Synthesis and STA | VLSI Mentors, Bengaluru |

| Duration of Training/Internship | Credits | |||||

|---|---|---|---|---|---|---|

| 2 Weeks | 1 | |||||

| 3 Weeks | 2 | |||||

| 8 Weeks& above | 3 | |||||

| S.No. | Academic Year | Name of the Industry | Duration | No.of Students | ||

|---|---|---|---|---|---|---|

| 1. | 2024-25 | Mspand Technologies Pvt.Ltd, Theni | 30.12.2024-11.01.2025 | 15 | View | |

| 2. | 2024-25 | Indira Gandhi Centre for Atomic Research [IGCAR],Kalpakkam | 20.05.2025-30.06.2025 | 7 | View | |

| S.No. | Academic Year | Name of the Industry | Duration | No.of Students | |

|---|---|---|---|---|---|

| 1. | 2025-26 | Mspand Technologies Pvt.Ltd, Theni | 23.06.2025-11.07.2025 | 15 | View |

| 2. | 2025-26 | VLSI Mentors | 20.06.2025-25.07.2025 | 30 | View |

Companies with us

Academic Laboratory

Lab In charge - Faculty & staff: Mr.D.Poornakumar & Mr.S.Gokul

Lab In charge - Faculty & staff: Dr.S.Pradeep & Mr.S.Gokul

Lab In charge - Faculty & staff: Mrs.C.Saranya & Mr.A.Elango

Lab In charge - Faculty & staff: Dr.S.Gomathi & Mrs.G.Tharani

Seminar Hall

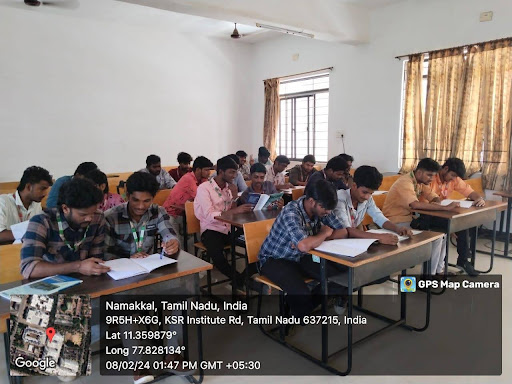

Class Rooms

No of classes : 4

No of classes : 2

Department Library

| S.No. | Particulars | Count |

|---|---|---|

| 1. | Ph.D. Doctorates | 3 |

| 2. | Ph.D. Supervisors | 1 |

| 3. | Ph.D. Pursuing | 2 |

| 8. | Ph.D. Completed | - |

| S.No. | Academic Year | Book Chapters | Journals | Conference | ||

|---|---|---|---|---|---|---|

| National | International | National | International | |||

| 1. | 2025-26 | - | - | 1 | - | 2 |

| 2. | 2024-25 | 4 | 2 | 5 | - | 11 |

| S.No. | Academic Year | Patents | Copyrights | |||

|---|---|---|---|---|---|---|

| Filed | Published | Granted | Filed | Granted | ||

| 1. | 2025-26 | 1 | - | - | - | - |

| 1. | 2024-25 | 13 | 12 | 2 | - | - |

| S.No. | Academic Year | Name of Faculty (Chief Consultant) | Client Organization | Title of the Project | Duration | Amount received(in Rupees) |

|---|---|---|---|---|---|---|

| 1. | 2024-25 | Dr.S.Gomathi | Arunai Creations | Sewing Machine board Automation and error correction service | 18.10.2024 to 20.10.2025 | 50,000 |

| 2. | 2024-25 | Dr.S.Gomathi | VSAN Electricals | VLSI Design of an Advanced Capacitive Proximity Sensor for Industrial Automation | 02.01.2025 to 18.03.2025 | 1,20,000 |

MOUs

| S. No. | Date of Signing | Name of the Company | Validity |

|---|---|---|---|

| ACADEMIC YEAR (2024 – 2025) | |||

| 1 | 01.11.2024 | VLSI Mentors,Bangalore | 3 Years |

| 2 | 18.10.2024 | Mspand Technologies Pvt.Ltd,Theni | 3 Years |

| S.No. | Academic Year | Number of Events | |

|---|---|---|---|

| 1. | 2025-26 | 2 | |

| 2. | 2024-25 | 12 |

S2S CLUB (Student 2 Skill)

S2S CLUB (Student 2 Skill)

- Faculty Coordinator: Mr.D.Poornakumar

- MEMBERS:

1. S.B.Tamilraja

2. S.Dharanisri

3. M.Sathyajeeva

4. M.Suriya Prasanth

5. D.Tharun

6. S.Chindu Sri

- Activities

| S.No. | Academic Year | Number of Events | |

|---|---|---|---|

| 1. | 2025-26 | 1 | |

| 2. | 2024-25 | 2 |

CSSR CLUB (Centre For Silicon System Research )

CSSR CLUB (Centre For Silicon System Research )

- Faculty Coordinator: C.Saranya

- MEMBERS:

1. M.Deepasri

2. S.Y.Omganesh

3. R.Vinoth

4. G.S.Harshaprabha

5. P.V.Sudharson

6. S.Kalaimagal

- Activities

| S.No. | Year | Number of Events | |

|---|---|---|---|

| 1. | 2025-26 | 1 | View |

| 2. | 2024-25 | 2 | View |

Industrial Visit

| S.No. | Date | Name of industry | No.of Students Visited |

|---|---|---|---|

| 1. | 20.09.2024 | ISRO, Bengaluru | 50(2023-27 Batch) |

| 2. | 20.09.2024 | Tessolve Semiconductor Pvt.Ltd, Bengaluru | 50(2023-27 Batch) |